英特尔的“维持生命”摩尔定律说,万亿次浮点运算的设计将在2030年实现

日期:2022-12-09 20:30:55 / 人气:430

半导体按照摩尔定律进化,大约两年性能翻倍。其驱动力是缩小晶体管尺寸等提高集成度的小型化技术。近年来,半导体行业关于摩尔定律可行性的争论时有发生,但半导体大厂英特尔依然是摩尔定律的坚定支持者。

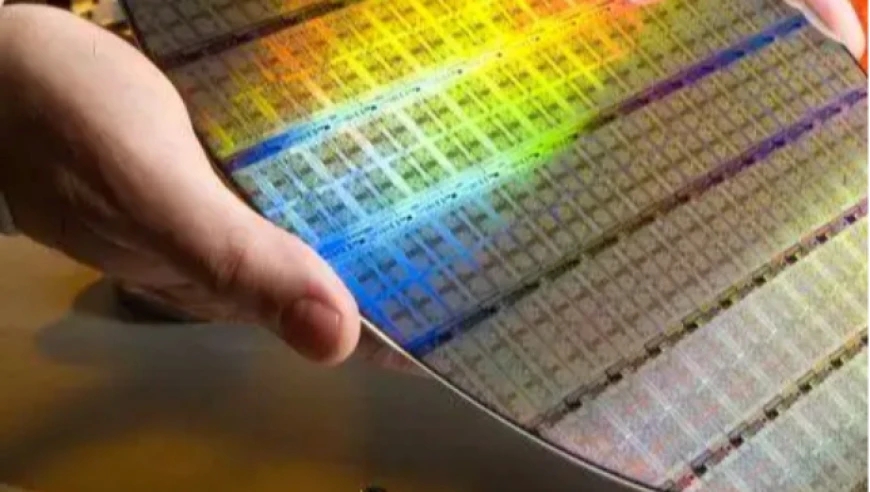

本周,在半导体行业大会IEDM 2022 (IEEE国际电子设备大会2022)上,英特尔发布了多篇论文,包括2D材料、3D封装技术、内存技术等多项技术进展。该公司还表示,未来十年将继续推广摩尔定律,预计到2030年单个封装中可集成一万亿个晶体管。

“目前,我们可以在单个封装中放置1000亿个晶体管,还有10倍需要增加。”12月8日,英特尔中国研究院院长宋继强在接受界面新闻等采访时表示。他说,从2023年到2030年,晶体管密度要在8年内提高10倍,也就是实现2的3次方的提升,这是一个相当激进的目标。

同时,目前半导体晶体管结构正从FinFET向GAAFET发展。与目前先进工艺使用的FinFET相比,GAAFET架构具有更好的静态特性,在相同尺寸下可以实现更高的频率和更低的功耗。所以GAAFET架构是目前3 nm等高端工艺的核心技术。宋继强指出,在GAAFET架构下进一步小型化,会导致漏电流、开关难控制等问题。使用传统硅材料作为沟道材料面临诸多挑战。

宋继强表示,要实现在单个封装中集成一万亿个晶体管的目标,一方面要继续依靠晶体管小型化,比如使用超薄的2D材料来制作效率更高的GAA晶体管。另一方面需要依靠3D封装技术,可以进一步提高整个设备的晶体管总数。

英特尔在IEDM发表的论文中涵盖了这两个方向。英特尔表示,新材料和新工艺模糊了封装和芯片制造之间的界限。与2021年发表的结果相比,通过混合键合技术,互连间距进一步减小到3微米,密度提高了10倍。同时,通过超薄的“2D”材料,即过渡金属硫化物,可以在单个芯片上集成更多的晶体管。

过去,在先进工艺技术的研究中,英特尔倾向于“单打独斗”,自己克服一切困难。由于英特尔近年来在先进工艺技术的竞争中落后于TSMC,它逐渐改变了策略。以先进封装技术的应用为例,宋继强表示,先进封装可以集成不同的小芯片。当涉及到一个芯片内不同小芯片的互连时,需要设计厂商、晶圆厂、封装厂、EDA工具厂商的合作来规范协议层面。此外,软件工具也需要升级以支持小芯片设计。

英特尔负责技术开发的副总裁安·凯莱赫(Ann Kelleher)本周表示,该公司已经完全步入正轨。英特尔目前有季度里程碑。从这些里程碑来看,公司是提前了,还是走上了正轨。她说,英特尔正在采取比过去更务实的方法,并建立应急计划,以确保不会出现重大延误。同时,该公司也更多地依赖设备供应商的帮助,而不是试图独自完成所有工作。

按照英特尔规划的进度,公司目前正在生产Intel 4(即7 nm)工艺,预计年底进入试产阶段。未来将用于第14代流星湖处理器架构,2023年下半年准备进入Intel 3(3 nm)制程工艺。外界普遍认为,首批产品将于2024年上半年出现。

作者:焦点注册登录平台

新闻资讯 News

- 通过放短视频来堆音量,这次被短...12-04

- 计算能力租赁价格暴涨,玩家涌入...12-04

- 三星CIS涨价30%,国内CIS厂...12-04

- 业带商,命运掌握在自己手里12-04